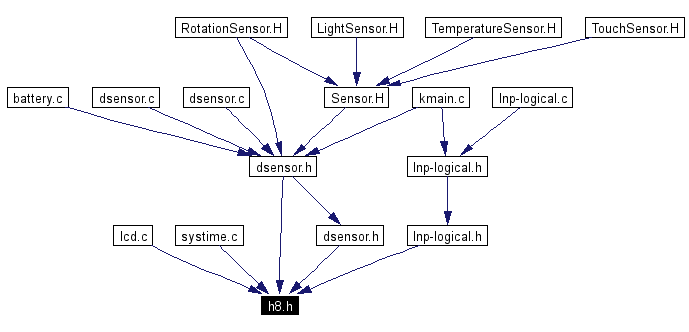

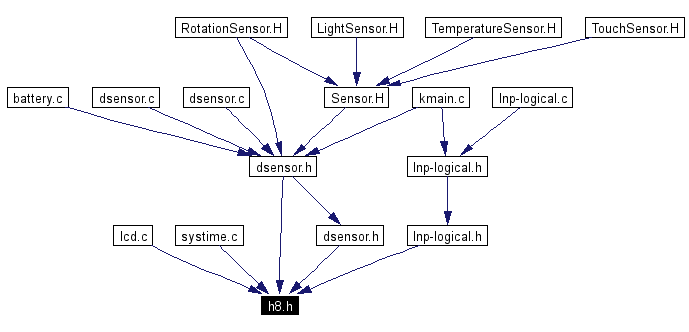

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Defines | |

| #define | TIER_ENABLE_ICA 0x80 |

| #define | TIER_ENABLE_ICB 0x40 |

| #define | TIER_ENABLE_ICC 0x20 |

| #define | TIER_ENABLE_ICD 0x10 |

| #define | TIER_ENABLE_OCA 0x08 |

| #define | TIER_ENABLE_OCB 0x04 |

| #define | TIER_ENABLE_OF 0x02 |

| #define | TIER_RESERVED 0x01 |

| #define | TCSR_ICA 0x80 |

| #define | TCSR_ICB 0x40 |

| #define | TCSR_ICC 0x20 |

| #define | TCSR_ICD 0x10 |

| #define | TCSR_OCA 0x08 |

| #define | TCSR_OCB 0x04 |

| #define | TCSR_OF 0x02 |

| #define | TCSR_RESET_ON_A 0x01 |

| #define | TCR_A_RISING 0x80 |

| #define | TCR_B_RISING 0x40 |

| #define | TCR_C_RISING 0x20 |

| #define | TCR_D_RISING 0x10 |

| #define | TCR_BUFFER_A 0x08 |

| #define | TCR_BUFFER_B 0x04 |

| #define | TCR_CLOCK_2 0x00 |

| #define | TCR_CLOCK_8 0x01 |

| #define | TCR_CLOCK_32 0x02 |

| #define | TCR_CLOCK_EXT 0x03 |

| #define | TOCR_OCRA 0x00 |

| #define | TOCR_OCRB 0x10 |

| #define | TOCR_ENABLE_A 0x08 |

| #define | TOCR_ENABLE_B 0x04 |

| #define | TOCR_HIGH_LEVEL_A 0x02 |

| #define | TOCR_HIGH_LEVEL_B 0x01 |

| #define | CR_ENABLE_IRQA 0x40 |

| #define | CR_ENABLE_IRQB 0x80 |

| #define | CR_ENABLE_IRQO 0x20 |

| #define | CR_CLEAR_NEVER 0x00 |

| #define | CR_CLEAR_ON_A 0x08 |

| #define | CR_CLEAR_ON_B 0x10 |

| #define | CR_CLEAR_ON_EXTERN 0x18 |

| #define | CSR_MATCH_A 0x40 |

| #define | CSR_MATCH_B 0x80 |

| #define | CSR_OVERFLOW 0x20 |

| #define | CSR_IGNORE_B 0x00 |

| #define | CSR_0_ON_B 0x04 |

| #define | CSR_1_ON_B 0x08 |

| #define | CSR_TOGGLE_ON_B 0x0c |

| #define | CSR_IGNORE_A 0x00 |

| #define | CSR_0_ON_A 0x01 |

| #define | CSR_1_ON_A 0x02 |

| #define | CSR_TOGGLE_ON_A 0x03 |

| #define | SMR_SYNC 0x80 |

| #define | SMR_ASYNC 0x00 |

| #define | SMR_7BIT 0x40 |

| #define | SMR_8BIT 0x00 |

| #define | SMR_P_NONE 0x00 |

| #define | SMR_P_EVEN 0x20 |

| #define | SMR_P_ODD 0x30 |

| #define | SMR_1STOP 0x00 |

| #define | SMR_2STOP 0x08 |

| #define | SMR_MP 0x04 |

| #define | SMR_CLOCK 0x00 |

| #define | SMR_CLOCK_4 0x01 |

| #define | SMR_CLOCK_16 0x02 |

| #define | SMR_CLOCK_64 0x03 |

| #define | SCR_TX_IRQ 0x80 |

| #define | SCR_RX_IRQ 0x40 |

| #define | SCR_TRANSMIT 0x20 |

| #define | SCR_RECEIVE 0x10 |

| #define | SCR_MP_IRQ 0x08 |

| #define | SCR_TE_IRQ 0x04 |

| #define | SCR_INT_CLOCK 0x00 |

| #define | SCR_EXT_CLOCK 0x02 |

| #define | SCR_CLOCK_OUT 0x01 |

| #define | SSR_TRANS_EMPTY 0x80 |

| #define | SSR_RECV_FULL 0x40 |

| #define | SSR_OVERRUN_ERR 0x20 |

| #define | SSR_FRAMING_ERR 0x10 |

| #define | SSR_PARITY_ERR 0x08 |

| #define | SSR_ERRORS 0x38 |

| #define | SSR_TRANS_END 0x04 |

| #define | SSR_MP 0x02 |

| #define | SSR_MP_TRANSFER 0x01 |

| #define | B2400 207 |

| #define | B4800 103 |

| #define | B9600 51 |

| #define | B19200 25 |

| #define | B38400 12 |

| #define | ADCSR_END 0x80 |

| #define | ADCSR_ENABLE_IRQ 0x40 |

| #define | ADCSR_START 0x20 |

| #define | ADCSR_SCAN 0x10 |

| #define | ADCSR_TIME_266 0x00 |

| #define | ADCSR_TIME_134 0x08 |

| #define | ADCSR_GROUP_0 0x00 |

| #define | ADCSR_GROUP_1 0x04 |

| #define | ADCSR_AN_0 0x00 |

| #define | ADCSR_AN_1 0x01 |

| #define | ADCSR_AN_2 0x02 |

| #define | ADCSR_AN_3 0x03 |

| #define | ADCR_EXTERN 0x80 |

| #define | SYSCR_SOFTWARE_STANDBY 0x80 |

| #define | WDT_CSR_PASSWORD (0xA500) |

| #define | WDT_CSR_ENABLE (0x0020) |

| #define | WDT_CSR_MODE_WATCHDOG (0x0040) |

| #define | WDT_CSR_MODE_OVERFLOW (0x0000) |

| #define | WDT_CSR_WATCHDOG_NMI (0x0000) |

| #define | WDT_CSR_WATCHDOG_RES (0x0008) |

| #define | WDT_CSR_CLOCK_2 (0x0000) |

| #define | WDT_CSR_CLOCK_32 (0x0001) |

| #define | WDT_CSR_CLOCK_64 (0x0002) |

| #define | WDT_CSR_CLOCK_128 (0x0003) |

| #define | WDT_CSR_CLOCK_256 (0x0004) |

| #define | WDT_CSR_CLOCK_512 (0x0005) |

| #define | WDT_CSR_CLOCK_2048 (0x0006) |

| #define | WDT_CSR_CLOCK_4096 (0x0007) |

| #define | WDT_CNT_PASSWORD (0x5A00) |

| #define | WDT_CNT_CLEAR (0x0000) |

| #define | WDT_CNT_MSEC_64 (0x0006) |

Variables | |

| unsigned char | T_IER |

| 16-bit timer interrupt enable register | |

| volatile unsigned char | T_CSR |

| 16-bit timer control / status register | |

| volatile unsigned | T_CNT |

| 16-bit timer count register | |

| unsigned | T_OCRA |

| 16-bit timer output compare register A | |

| unsigned | T_OCRB |

| 16-bit timer output compare register B | |

| unsigned char | T_CR |

| 16-bit timer control register | |

| unsigned char | T_OCR |

| 16-bit timer output control register | |

| volatile unsigned | T_ICRA |

| 16-bit timer input capture A register | |

| volatile unsigned | T_ICRB |

| 16-bit timer input capture B register | |

| volatile unsigned | T_ICRC |

| 16-bit timer input capture C register | |

| volatile unsigned | T_ICRD |

| 16-bit timer input capture D register | |

| unsigned char | STCR |

| serial / timer control register | |

| unsigned char | T0_CR |

| timer 0 control register | |

| volatile unsigned char | T0_CSR |

| timer 0 control / status register | |

| unsigned char | T0_CORA |

| timer 0 constant A register | |

| unsigned char | T0_CORB |

| timer 0 constant B register | |

| volatile unsigned char | T0_CNT |

| timer 0 counter register | |

| unsigned char | T1_CR |

| timer 1 control register | |

| volatile unsigned char | T1_CSR |

| timer 1 control / status register | |

| unsigned char | T1_CORA |

| timer 1 constant A register | |

| unsigned char | T1_CORB |

| timer 1 constant B register | |

| volatile unsigned char | T1_CNT |

| timer 1 counter register | |

| volatile unsigned char | S_RDR |

| serial receive data register | |

| unsigned char | S_TDR |

| serial transmit data register | |

| unsigned char | S_MR |

| serial mode register | |

| unsigned char | S_CR |

| serial control register | |

| volatile unsigned char | S_SR |

| serial status register | |

| unsigned char | S_BRR |

| serial baud rate register | |

| unsigned char | S_TCR |

| serial / timer control register | |

| volatile unsigned char | AD_A_H |

| A/D converter data register A high. | |

| volatile unsigned char | AD_A_L |

| A/D converter data register A low. | |

| volatile unsigned char | AD_B_H |

| A/D converter data register B high. | |

| volatile unsigned char | AD_B_L |

| A/D converter data register B low. | |

| volatile unsigned char | AD_C_H |

| A/D converter data register C high. | |

| volatile unsigned char | AD_C_L |

| A/D converter data register C low. | |

| volatile unsigned char | AD_D_H |

| A/D converter data register D high. | |

| volatile unsigned char | AD_D_L |

| A/D converter data register D low. | |

| volatile unsigned | AD_A |

| A/D converter data register A. | |

| volatile unsigned | AD_B |

| A/D converter data register B. | |

| volatile unsigned | AD_C |

| A/D converter data register C. | |

| volatile unsigned | AD_D |

| A/D converter data register D. | |

| volatile unsigned char | AD_CSR |

| A/D converter control / status register. | |

| unsigned char | AD_CR |

| A/D converter control register. | |

| unsigned char | SYSCR |

| system control register | |

| unsigned char | PORT1_PCR |

| port 1 input pull-up control register | |

| unsigned char | PORT2_PCR |

| port 2 input pull-up control register | |

| unsigned char | PORT3_PCR |

| port 3 input pull-up control register | |

| unsigned char | PORT1_DDR |

| port 1 data direction register | |

| volatile unsigned char | PORT1 |

| port 1 I/O register | |

| unsigned char | PORT2_DDR |

| port 2 data direction register | |

| volatile unsigned char | PORT2 |

| port 2 I/O register | |

| unsigned char | PORT3_DDR |

| port 3 data direction register | |

| volatile unsigned char | PORT3 |

| port 3 I/O register | |

| unsigned char | PORT4_DDR |

| port 4 data direction register | |

| volatile unsigned char | PORT4 |

| port 4 I/O register | |

| unsigned char | PORT5_DDR |

| port 5 data direction register | |

| volatile unsigned char | PORT5 |

| port 5 I/O register | |

| unsigned char | PORT6_DDR |

| port 6 data direction register | |

| volatile unsigned char | PORT6 |

| port 6 I/O register | |

| volatile unsigned char | PORT7 |

| port 7 input register | |

| volatile unsigned int | WDT_CSR |

| watch dog timer control register | |

| volatile unsigned char | WDT_CNT |

| watch dog timer counter register | |

Definition in file h8.h.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Definition at line 106 of file h8.h. Referenced by systime_init(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Definition at line 93 of file h8.h. Referenced by systime_init(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Definition at line 78 of file h8.h. Referenced by systime_init(), and systime_shutdown(). |

|

|

Definition at line 79 of file h8.h. Referenced by systime_init(), and systime_shutdown(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Definition at line 112 of file h8.h. Referenced by systime_init(). |

|

|

Definition at line 113 of file h8.h. Referenced by systime_init(). |

|

|

|

|

|

Definition at line 448 of file h8.h. Referenced by systime_init(). |

|

|

Definition at line 446 of file h8.h. Referenced by systime_init(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Definition at line 436 of file h8.h. Referenced by systime_init(). |

|

|

Definition at line 429 of file h8.h. Referenced by systime_init(), and systime_shutdown(). |

|

|

|

|

|

Definition at line 430 of file h8.h. Referenced by systime_init(). |

|

|

Definition at line 428 of file h8.h. Referenced by systime_init(). |

|

|

Definition at line 432 of file h8.h. Referenced by systime_init(). |

|

|

|

|

|

A/D converter data register A. bits 0..5 reserved, probably zero |

|

|

A/D converter data register A high.

|

|

|

A/D converter data register A low. bits 0..5 reserved, probably zero |

|

|

A/D converter data register B. bits 0..5 reserved, probably zero |

|

|

A/D converter data register B high.

|

|

|

A/D converter data register B low. bits 0..5 reserved, probably zero |

|

|

A/D converter data register C. bits 0..5 reserved, probably zero |

|

|

A/D converter data register C high.

|

|

|

A/D converter data register C low. bits 0..5 reserved, probably zero |

|

|

A/D converter control register.

|

|

|

A/D converter control / status register.

|

|

|

A/D converter data register D. bits 0..5 reserved, probably zero |

|

|

A/D converter data register D high.

|

|

|

A/D converter data register D low. bits 0..5 reserved, probably zero |

|

|

port 1 I/O register

|

|

|

port 1 data direction register

|

|

|

port 1 input pull-up control register

|

|

|

port 2 I/O register

|

|

|

port 2 data direction register

|

|

|

port 2 input pull-up control register

|

|

|

port 3 I/O register

|

|

|

port 3 data direction register

|

|

|

port 3 input pull-up control register

|

|

|

port 4 I/O register

Definition at line 403 of file h8.h. Referenced by lnp_logical_range(), and lnp_logical_range_is_far(). |

|

|

port 4 data direction register

|

|

|

port 5 I/O register

|

|

|

port 5 data direction register

|

|

|

port 6 I/O register

Definition at line 417 of file h8.h. Referenced by ds_passive(). |

|

|

port 6 data direction register

Definition at line 414 of file h8.h. Referenced by i2c_read_ack(), and lcd_init(). |

|

|

port 7 input register

|

|

|

serial baud rate register

|

|

|

serial control register

|

|

|

serial mode register

|

|

|

serial receive data register

|

|

|

serial status register

|

|

|

serial / timer control register

|

|

|

serial transmit data register

|

|

|

serial / timer control register

|

|

|

system control register

|

|

|

timer 0 counter register

|

|

|

timer 0 constant A register

|

|

|

timer 0 constant B register

|

|

|

timer 0 control register

|

|

|

timer 0 control / status register

|

|

|

timer 1 counter register

|

|

|

timer 1 constant A register

|

|

|

timer 1 constant B register

|

|

|

timer 1 control register

|

|

|

timer 1 control / status register

|

|

|

16-bit timer count register

|

|

|

16-bit timer control register

Definition at line 53 of file h8.h. Referenced by systime_init(). |

|

|

16-bit timer control / status register

Definition at line 40 of file h8.h. Referenced by systime_init(). |

|

|

16-bit timer input capture A register

|

|

|

16-bit timer input capture B register

|

|

|

16-bit timer input capture C register

|

|

|

16-bit timer input capture D register

|

|

|

16-bit timer interrupt enable register

Definition at line 37 of file h8.h. Referenced by systime_init(), and systime_shutdown(). |

|

|

16-bit timer output control register

Definition at line 56 of file h8.h. Referenced by systime_init(). |

|

|

16-bit timer output compare register A

Definition at line 46 of file h8.h. Referenced by systime_init(). |

|

|

16-bit timer output compare register B

Definition at line 50 of file h8.h. Referenced by systime_init(). |

|

|

watch dog timer counter register

|

|

|

watch dog timer control register

Definition at line 426 of file h8.h. Referenced by systime_init(), and systime_shutdown(). |

|

brickOS is released under the

Mozilla Public License.

Original code copyright 1998-2002 by the authors. |

1.3.5

1.3.5